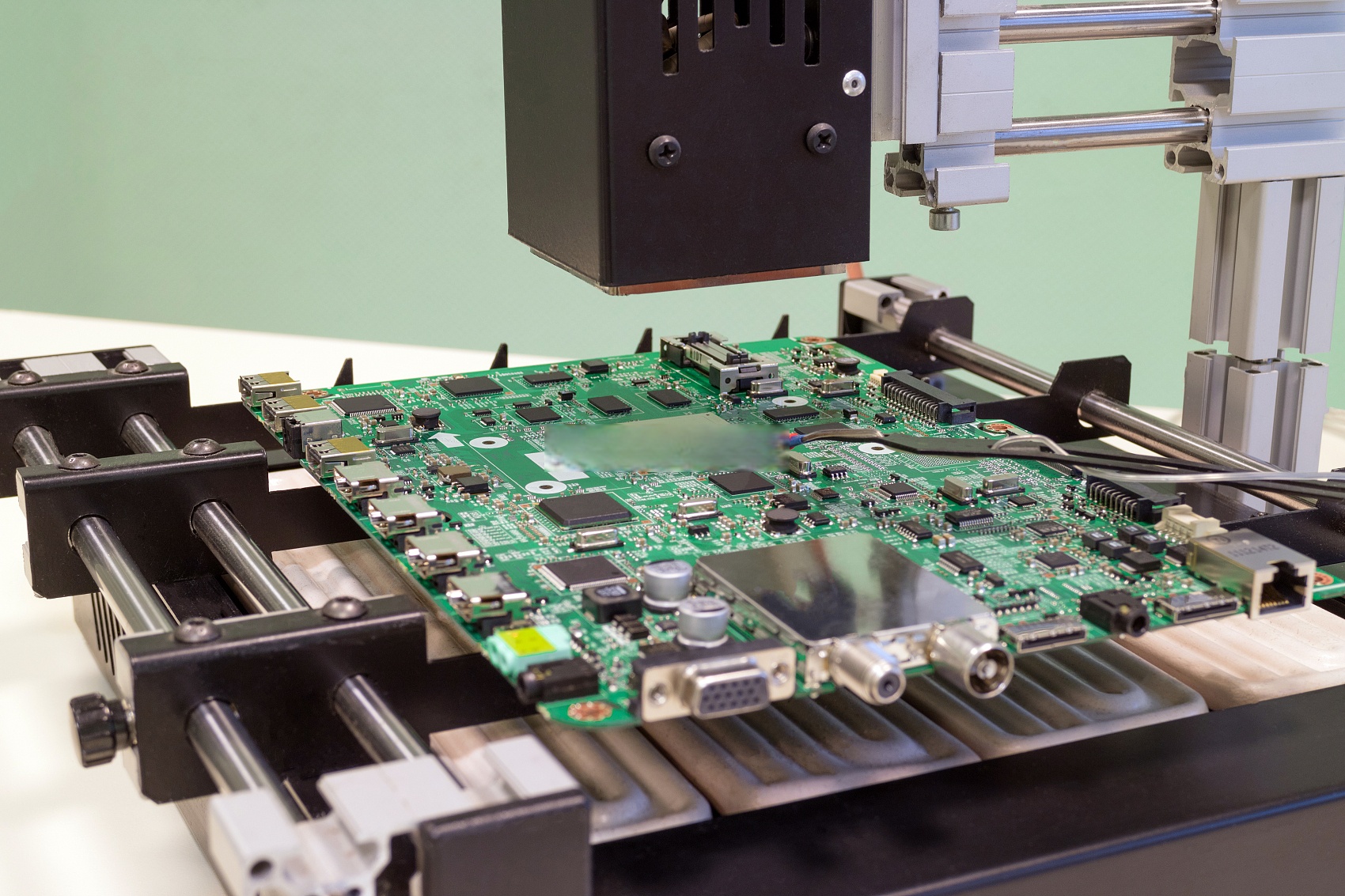

在我国半导体产业向 “自主可控” 迈进的过程中,芯片制造的每一个环节都至关重要 —— 从纳米级电路的刻蚀到导电互联的搭建,再到元件的防护与绝缘,都离不开对 “薄膜” 的精准控制。真空镀膜设备作为半导体产业的 “核心装备”,能在晶圆表面制备厚度仅几纳米到几十纳米的功能薄膜,像 “原子级工匠” 一样搭建芯片的 “骨架” 与 “神经”,解决了传统工艺无法实现的 “高精度、高纯度、高均匀性” 难题,成为推动我国半导体技术突破的关键力量。下面就详细拆解真空镀膜设备在半导体产业中的应用、优势及发展前景。

一、三大核心应用:真空镀膜设备贯穿芯片制造全流程

半导体芯片的制造流程复杂,涉及数十道工序,而真空镀膜设备主要在 “薄膜沉积” 环节发挥作用,为芯片打造导电、绝缘、防护等关键功能层,核心应用集中在三个领域:

1. 互联层制备:搭建芯片的 “电流通道”

芯片内部需要大量 “导线”(互联层)连接晶体管,实现电流传输,传统金属蒸发工艺无法满足纳米级互联的需求,真空镀膜设备通过两种核心工艺实现高精度互联:

• 物理气相沉积(PVD):采用磁控溅射工艺,在晶圆表面沉积铜、铝等金属薄膜(厚度 20-50 纳米)作为互联导线。设备通过高真空环境(10⁻⁷帕以上)和精准的靶材控制,确保金属薄膜纯度达 99.999% 以上,且均匀性误差<1%—— 避免因杂质导致的电流损耗,或因厚度不均引发的电路短路。例如,7 纳米芯片的铜互联层,需通过 PVD 设备沉积 5 层以上薄膜,每层厚度误差控制在 ±0.5 纳米,才能保证芯片的稳定运行;

• 化学气相沉积(CVD):针对更精细的互联结构(如通孔、沟槽),采用 CVD 工艺沉积钨薄膜作为 “塞子”(填充通孔),设备通过控制反应气体(如六氟化钨)的浓度与温度,让钨原子均匀填充微小空间,避免出现空隙,确保电流顺畅通过。

2. 绝缘与介质层制备:打造芯片的 “绝缘屏障”

芯片中晶体管与互联层之间需要绝缘层隔离,防止电流泄漏,真空镀膜设备通过制备高质量介质薄膜实现这一功能:

• 高 K 介质膜:传统二氧化硅绝缘膜在纳米级工艺下漏电严重,真空镀膜设备采用原子层沉积(ALD)工艺,在晶圆表面沉积氧化铪(HfO₂)等高 K 介质膜(厚度 3-5 纳米)。ALD 工艺可实现 “原子级逐层沉积”,薄膜致密无孔隙,漏电率比二氧化硅降低 1000 倍以上,支撑 5 纳米、3 纳米先进制程芯片的研发;

• 隔离层与钝化层:在芯片制造后期,需用 CVD 设备沉积氮化硅(Si₃N₄)、氧化硅(SiO₂)薄膜作为隔离层(分隔不同电路模块)和钝化层(保护芯片表面)。这些薄膜能阻挡水汽、杂质入侵,同时避免芯片在封装过程中受损,确保芯片长期稳定工作。

3. 电极与接触层制备:实现芯片的 “内外连接”

芯片需要通过电极与外部电路(如 PCB 板)连接,真空镀膜设备为电极制备提供关键支撑:

• 金属电极沉积:采用电子束蒸发工艺,在芯片表面沉积金、银、钯等金属薄膜(厚度 100-200 纳米)作为电极。设备通过精准控制蒸发速率(0.1-1 纳米 / 秒),确保电极表面平整光滑,降低接触电阻,避免因电阻过高导致的芯片发热或性能衰减;

• 欧姆接触层制备:在晶体管与互联层的接触部位,需沉积 “金属 - 半导体复合膜”(如钛 - 硅合金膜)作为欧姆接触层,降低接触电阻。真空镀膜设备通过 PVD 工艺实现金属与半导体的精准混合,确保接触电阻<10⁻⁶欧・厘米,提升芯片的电流传输效率。

二、四大核心优势:真空镀膜设备为何成为半导体产业的 “刚需”?

相较于蒸发、溅射等传统薄膜制备技术,真空镀膜设备在半导体领域的优势极为显著,完美契合芯片制造对 “高精度、高纯度、高稳定性” 的需求:

1. 精度更高:满足纳米级制程需求

半导体芯片的制程已进入 3 纳米、2 纳米时代,对薄膜厚度的控制精度要求达到 ±0.1 纳米。真空镀膜设备通过 ALD、高精度 PVD 等工艺,可实现原子级的薄膜厚度控制,且均匀性误差<1%—— 例如,ALD 设备每沉积一层薄膜,厚度仅增加 0.1-0.5 纳米,相当于 1-5 个原子的直径,能精准匹配先进制程芯片的需求;而传统蒸发工艺的厚度误差常超 5%,无法满足 7 纳米以下制程的要求。

2. 纯度更高:避免杂质影响芯片性能

芯片中的杂质会严重影响晶体管的开关速度和稳定性,甚至导致芯片失效。真空镀膜设备的镀膜过程在高真空环境(10⁻⁵-10⁻⁹帕)中进行,可有效去除空气中的氧气、水分、灰尘等杂质,制备的薄膜纯度达 99.999% 以上(5N 级别);同时,设备采用高纯度靶材(如 6N 级铜靶、铝靶),进一步减少杂质引入。而传统电镀工艺易引入金属离子、有机物等杂质,纯度难以突破 99.9%(3N 级别)。

3. 兼容性更强:适配多样材料与结构

半导体芯片涉及金属(铜、铝、钨)、氧化物(氧化铪、氧化硅)、氮化物(氮化硅)等多种材料,且结构复杂(包含平面、沟槽、通孔等)。真空镀膜设备可通过调整工艺参数(如温度、压力、气体种类),适配不同材料的沉积需求 —— 例如,PVD 设备可沉积金属与金属合金,CVD 设备可沉积非金属化合物,ALD 设备可在复杂三维结构表面实现均匀镀膜;而传统工艺往往只能适配单一材料或简单结构,兼容性较差。

4. 稳定性更好:保障芯片量产一致性

半导体产业对芯片的量产一致性要求极高,同一批次芯片的性能差异需控制在 5% 以内。真空镀膜设备通过自动化控制系统(如 PLC、AI 算法),可实现工艺参数的精准复现,确保每片晶圆的镀膜效果一致;同时,设备配备实时监测系统(如石英晶体振荡、椭圆偏振仪),可实时调整工艺参数,避免因设备老化、靶材损耗导致的性能波动。而传统工艺依赖人工操作,一致性难以保障,批次间差异常超 10%。

三、发展前景:三大趋势推动真空镀膜设备 “升级迭代”

随着我国半导体产业的快速发展(2025 年市场规模预计突破 5000 亿元),以及先进制程、特色工艺的不断突破,真空镀膜设备将迎来三大发展趋势:

1. 向 “更先进制程” 突破:适配 3 纳米及以下工艺

目前,国际主流真空镀膜设备已能支撑 3 纳米制程,而我国在 14 纳米、7 纳米制程设备上已实现部分突破,未来将向 3 纳米及以下制程进军:

• 研发更精准的 ALD 设备,实现 0.1 纳米以下的厚度控制,满足 2 纳米制程对高 K 介质膜、金属电极的需求;

• 开发 “PVD+ALD” 复合工艺设备,结合两种工艺的优势,在三维晶体管(如 GAA 纳米片晶体管)表面制备均匀的功能薄膜,解决先进制程的 “三维镀膜” 难题。

2. 向 “更大尺寸晶圆” 适配:满足 8 英寸、12 英寸晶圆需求

目前,12 英寸晶圆已成为半导体芯片的主流衬底,而我国部分特色工艺(如功率半导体)仍采用 8 英寸晶圆。真空镀膜设备将向 “大尺寸兼容” 方向升级:

• 扩大设备腔体尺寸,适配 12 英寸晶圆的镀膜需求,同时确保大面积晶圆的均匀性(边缘与中心的厚度差异<1%);

• 开发 “多晶圆同时处理” 设备,提升量产效率 —— 例如,传统设备单次处理 1 片 12 英寸晶圆,升级后可单次处理 2-4 片,产能提升 2-4 倍,降低芯片制造成本。

3. 向 “国产化自主可控” 迈进:突破 “卡脖子” 技术

我国在真空镀膜设备的核心部件(如高精度真空泵、靶材、监测传感器)上仍存在部分依赖进口的情况,未来将加速国产化进程:

• 研发国产高精度真空泵(如分子泵、离子泵),实现真空度 10⁻⁹帕以上的稳定控制,替代进口产品;

• 开发国产靶材与设备的适配技术,确保国产铜靶、铝靶在国产镀膜设备上的使用效果,达到进口靶材的性能水平;

• 建立 “设备 - 工艺 - 材料” 一体化产业链,推动国内设备企业与晶圆厂、材料厂商合作,联合开发适配我国半导体产业需求的真空镀膜设备,摆脱对进口设备的依赖。

总结:真空镀膜设备是半导体产业的 “核心基石”

从 7 纳米芯片的互联层搭建,到功率半导体的绝缘层制备,再到 MEMS 器件的电极沉积,真空镀膜设备已深度融入半导体制造的全流程,成为我国半导体产业实现 “自主可控” 的关键装备。随着先进制程的突破、大尺寸晶圆的普及以及国产化技术的成熟,真空镀膜设备将继续发挥 “芯片筑造师” 的作用,推动我国半导体产业从 “跟跑” 向 “并跑”“领跑” 转变,为全球半导体产业贡献 “中国方案”。

客服1

客服1