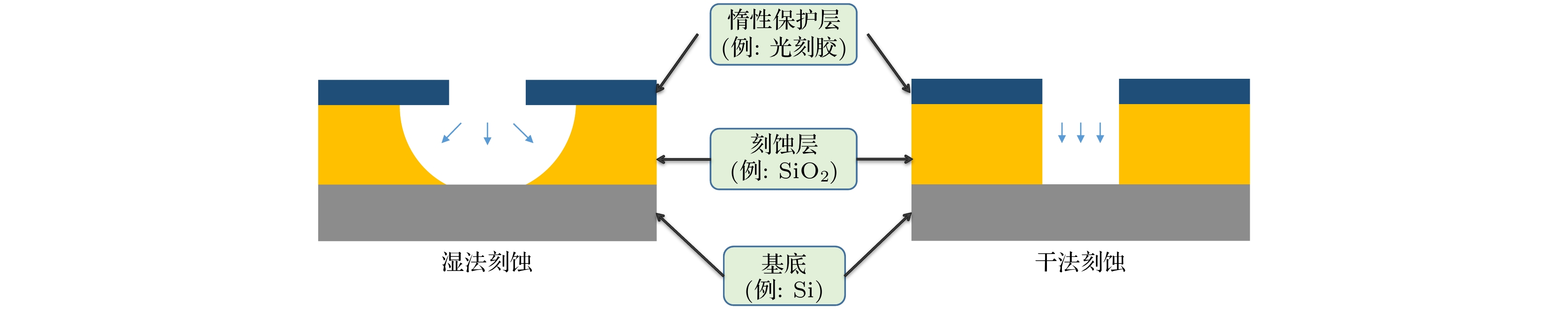

在半导体产业追求高性能、小尺寸的进程中,产品可靠性是核心竞争力。无论是车规芯片还是航天器件,均需在严苛工况下长期稳定运行。反应离子刻蚀机(RIE)作为 “微观雕刻” 核心工具,其刻蚀稳定性与精准度,直接决定器件结构完整性、电学一致性,进而影响使用寿命。以下从刻蚀参数调控、表面处理优化、设备维护监控三方面,解析如何通过 RIE 优化筑牢半导体可靠性根基。

一、精准调控刻蚀参数:从源头减少隐患

通过精细化调节关键参数,可在实现高精度刻蚀的同时,避免工艺波动引入结构缺陷,降低可靠性风险。

(一)刻蚀气体配比:平衡选择性与稳定性

气体配比直接影响刻蚀速率、材料选择性及结构化学稳定性。例如:

• 刻蚀硅基浅沟槽隔离(STI)时,纯 SF₆易致侧壁晶格损伤,加入适量 O₂可形成氧化硅保护层,减少损伤并提升光刻胶选择性;

• 刻蚀 GaN 功率器件源漏沟槽时,Cl₂/BCl₃比例需严控 —— 过高 BCl₃易残留硼化物引发漏电,调至 1:0.8 并搭配 Ar 等离子体清洗,可保障欧姆接触稳定,延长器件寿命。

(二)射频功率与反应压力:控制 “力度” 与均匀性

• 射频功率:决定离子能量。功率过高易致 “过刻蚀” 或侧壁粗糙,过低则刻蚀不均、残留残膜(引发后续接触不良)。如物联网压力传感器的 2μm 硅膜片,功率波动 ±5W 会使厚度偏差超 0.1μm(测量误差增 10%);采用 “低功率(100W)初始刻蚀 - 中功率(150W)提速率 - 低功率(80W)精修” 分段控制,可将偏差压至 0.03μm 内,确保 - 40℃~85℃下精度稳定性超 95%。

• 反应压力:影响离子平均自由程,调节刻蚀各向异性。刻蚀高深宽比(>10:1)通孔时,压力>10Pa 易致底部刻蚀不充分;降至 2~3Pa 可增加离子自由程,实现垂直刻蚀,避免侧壁 “扩孔”,使金属填充良率从 88% 升至 99.5%,减少漏电、信号延迟问题。

二、优化刻蚀后表面处理:消除 “隐性损伤”

即使参数精准,刻蚀后仍可能残留晶格缺陷、化学残留、表面电荷等 “隐性损伤”,若不消除会逐步引发性能衰减。

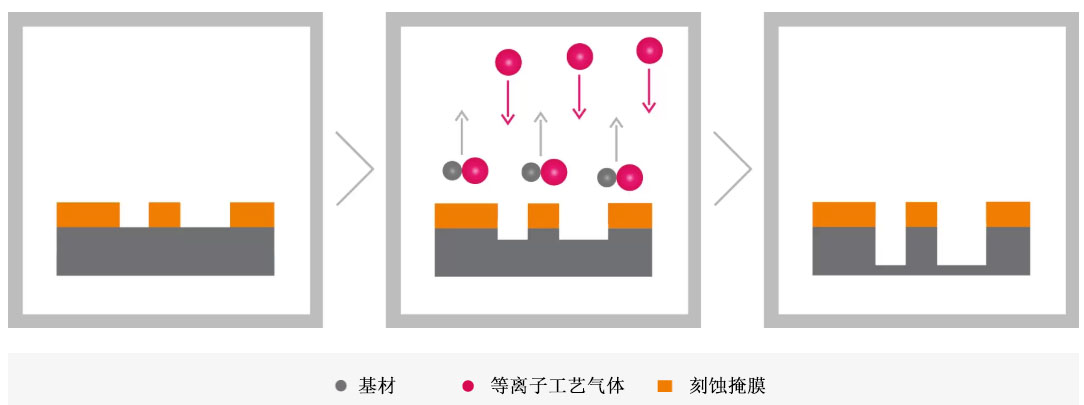

(一)等离子体清洗:去残留、修晶格

利用氢自由基、氩离子的清洁与修复作用:

• 刻蚀栅极氧化层(SiO₂)后,表面氟残留易与多晶硅栅极反应致漏电,通入 H₂等离子体可生成易挥发 HF,将氟残留降至 10¹⁰ atoms/cm² 以下;

• 针对硅晶格错位,200℃低温氢等离子体退火可形成稳定 Si-H 键,修复缺陷 —— 某厂商数据显示,此工艺使硅基器件反向漏电流降一个数量级,“双 85”(85℃、85% 湿度)测试失效概率从 0.8% 降至 0.1%。

(二)表面钝化:构建防护屏障

对恶劣环境(高温、高湿、强辐射)下的器件,钝化处理是最后防线。例如:

汽车发动机控制芯片的铝互连引线,刻蚀后表面氧化层 / 划痕易引发 “电迁移”(高温振动下引线断裂);通过 RIE 沉积 50nm 氮化硅(Si₃N₄)钝化层(硅烷 + 氨气等离子体反应),可耐高温、抗腐蚀并抑制铝迁移,使 150℃、1mA/μm² 工况下的引线寿命从 1000 小时延至 5000 小时,满足 “15 年 / 20 万公里” 车规要求。

三、强化设备维护与工艺监控:保障长期稳定

RIE 长期稳定运行是刻蚀一致性的基础,设备损耗、参数漂移若未及时处理,会累积为系统性误差,降低批量产品可靠性。

(一)关键部件预防性维护

针对影响刻蚀稳定的核心部件,制定维护方案:

• 射频电源:电容老化致功率波动(±2W→±8W),每 6 个月检测,老化超 10% 更换;

• 真空系统:密封圈老化致真空度下降(10⁻⁵ Pa→10⁻³ Pa),引入杂质,每月查密封性、每 3 个月换金属密封圈;

• 气体流量控制器(MFC):精度偏差超 2% 致配比偏离,每季度校准,确保精度 ±1% 内。

某代工厂实施后,设备非计划停机从每月 8 小时降至 2 小时,工艺波动减 60%,芯片可靠性合格率从 92% 升至 98.5%。

(二)实时监控与数据追溯

• 用光学发射光谱(OES)传感器实时监测等离子体谱线(如硅 288nm、氟 703nm),异常波动时自动报警停机,避免批量损失;

• 建 “工艺 - 设备 - 可靠性” 关联数据库,便于追溯优化。例如某批次 1% 失效芯片,追溯发现刻蚀于真空度轻微下降(10⁻⁵ Pa→5×10⁻⁵ Pa)时段,后续缩短密封圈更换周期并加预警阈值,同类失效降至 0.05%。

结语

RIE 过程优化是半导体可靠性的核心保障。从参数调控、表面处理到设备监控,每环节优化均为产品稳定性 “添砖加瓦”。随着制程向 3nm 及以下、应用向车规 / 航天延伸,未来结合 AI 参数自优化、数字孪生仿真,RIE 将从 “精准控制” 迈向 “智能优化”,进一步强化半导体可靠性。

客服1

客服1