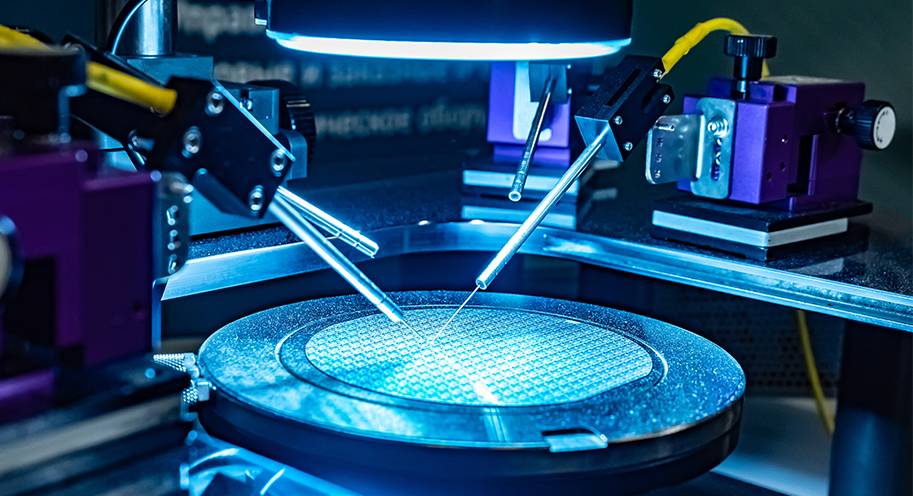

在半导体行业中,芯片的性能升级离不开 “微观层面” 的材料突破 —— 从 7nm 制程到 3nm 甚至 2nm,每一次制程跃迁,都对核心材料的纯度、精度、稳定性提出更严苛要求。而溅射靶材,作为物理气相沉积(PVD)技术制备芯片关键薄膜的 “原料核心”,直接决定着芯片互连层的导电性、绝缘层的可靠性、接触层的稳定性,是支撑半导体行业从 “成熟制程” 向 “先进制程” 迈进的关键材料。今天,我们就深入探讨溅射靶材在半导体行业的核心应用,以及其对行业进步的重要性。

一、核心应用:溅射靶材支撑半导体芯片三大关键薄膜制备

半导体芯片的结构复杂,从衬底到顶层金属,需通过多道 PVD 工艺沉积不同功能的薄膜,而每类薄膜的制备,都依赖特定性能的溅射靶材,其应用可聚焦于三大关键环节:

1. 互连层薄膜:铜靶为主力,决定芯片 “信号传输效率”

芯片的互连层相当于 “信息高速公路”,负责连接芯片内部的晶体管与外部电路,其导电性与可靠性直接影响芯片的运算速度与寿命,核心依赖铜靶与阻挡层靶材:

• 铜靶:实现低电阻互连

随着制程进入 14nm 以下,传统铝互连因电阻高、电迁移风险大逐步被铜替代。半导体用铜靶需具备极高纯度(99.999% 以上,即 5N 级,先进制程需 6N 级)与均匀微观结构(晶粒尺寸偏差<10%),通过 PVD 工艺沉积的铜互连层,电阻率可低至 1.7×10⁻⁸Ω・m(接近铜的理论电阻率),比铝互连低 30%,能有效减少信号延迟,支撑 3nm 制程芯片每秒百亿次的运算需求;

• 阻挡层靶材:防止铜扩散

铜原子易向芯片的绝缘层(如 SiO₂)扩散,导致电路漏电,需在铜互连层与绝缘层之间沉积阻挡层。常用的阻挡层靶材为钽靶(Ta)、钛靶(Ti),同样需高纯度(5N 级以上),通过 PVD 制备的 5-10nm 钽阻挡层,能有效抑制铜扩散(扩散系数<10⁻²⁰cm²/s),确保芯片在高温工作环境下(125℃以上)长期稳定,无漏电风险。

某芯片制造企业数据显示:采用 6N 级高纯度铜靶与钽靶制备的 3nm 制程芯片,互连层良率从 82% 提升至 95%,信号延迟降低 15%,芯片使用寿命延长至 10 年以上,远超行业标准的 7 年。

2. 绝缘层与介质层薄膜:氧化物 / 氮化物靶材,保障芯片 “电气隔离”

芯片内部需通过绝缘层、介质层实现不同电路的电气隔离,避免信号干扰,核心依赖氧化硅、氮化硅等陶瓷靶材:

• 氧化硅靶材(SiO₂):制备基础绝缘层

氧化硅靶材需高致密度(≥98%)与低杂质(金属杂质<1ppm),通过 PVD 沉积的氧化硅绝缘层,介电常数低(≈3.9)、击穿电压高(>10MV/cm),能有效隔离相邻电路,避免漏电与信号串扰,适配从成熟制程(90nm)到先进制程(3nm)的绝缘需求;

• 氮化硅靶材(Si₃N₄):制备高性能介质层

在芯片的电容器、钝化层等环节,需用氮化硅靶材制备介质层。氮化硅靶材沉积的薄膜介电常数高(≈7.5)、耐腐蚀性强,能提升电容器的容量密度(比氧化硅介质高 1 倍以上),同时保护芯片表面免受水汽、杂质侵蚀,提升芯片的环境适应性。

3. 接触层与电极薄膜:钛 / 铝 / 钨靶材,实现 “晶体管与互连的衔接”

芯片的接触层负责连接晶体管与互连层,电极则负责芯片与外部封装的连接,需具备低接触电阻、高附着力,核心依赖钛靶、铝靶、钨靶:

• 钛靶(Ti):制备接触层 “黏合剂”

钛靶沉积的钛薄膜能与硅衬底形成稳定的硅化钛(TiSi₂),同时与后续的铝或铜互连层紧密结合,起到 “黏合” 作用,接触电阻可低至 10⁻⁷Ω・cm²,确保晶体管信号高效传递至互连层;

• 铝靶(Al):成熟制程电极主力

在 90nm 及以上成熟制程中,铝靶仍是电极制备的主流选择,其成本低于铜靶,通过 PVD 沉积的铝电极薄膜,导电性稳定(电阻率≈2.7×10⁻⁸Ω・m),适配汽车电子、消费电子等对成本敏感的半导体领域;

• 钨靶(W):先进制程 “通孔填充” 专用

在 3D NAND、先进逻辑芯片中,需通过钨靶制备 “通孔电极”(连接不同层的互连),钨靶沉积的钨薄膜熔点高(3422℃)、抗电迁移性能强,能在微小通孔(直径<10nm)内实现均匀填充,保障多层互连的可靠性。

二、重要性:溅射靶材是半导体行业进步的 “关键推手”

溅射靶材对半导体行业的重要性,不仅体现在 “材料支撑”,更在于其技术突破直接推动芯片制程迭代、性能升级与成本优化,是行业进步不可或缺的 “微观基石”:

1. 靶材纯度与精度突破,支撑芯片制程向 “更小尺寸” 迭代

芯片制程从 7nm 到 3nm 再到 2nm,核心挑战之一是 “微观结构的精准控制”,而溅射靶材的纯度与精度直接决定了薄膜的质量下限:

• 3nm 制程芯片的互连层厚度仅 10-15nm,若靶材纯度不足(如含 0.5ppm 以上杂质),杂质原子会在薄膜中形成 “缺陷中心”,导致电路漏电率上升 50% 以上,无法满足芯片可靠性要求;

• 先进制程对靶材的 “微观均匀性” 要求极高(晶粒尺寸偏差<5%),若靶材晶粒不均,沉积的薄膜会出现局部厚度偏差(>±1nm),导致互连层电阻波动,影响芯片运算速度的稳定性。

可以说,没有 6N 级高纯度、高均匀性溅射靶材的突破,3nm 及以下先进制程芯片的量产将无从谈起。

2. 靶材性能优化,推动芯片 “更高性能与更低功耗”

半导体行业的核心追求是 “更高性能、更低功耗”,而溅射靶材通过性能优化,直接助力这一目标实现:

• 铜靶替代铝靶后,芯片互连层电阻降低 30%,信号延迟减少 20%,同等运算速度下,芯片功耗降低 15%,适配手机、笔记本等移动设备的 “长续航” 需求;

• 钽靶与铜靶的搭配使用,使芯片互连层的电迁移寿命从铝互连的 1000 小时延长至 10000 小时以上,芯片长期工作的稳定性提升,故障率降低 80%,满足服务器、数据中心对芯片 “高可靠性” 的要求。

3. 靶材国产化突破,保障半导体行业 “供应链安全”

长期以来,全球半导体用高端溅射靶材(如 6N 级铜靶、钽靶)主要由日本 JX 金属、美国霍尼韦尔等外资企业垄断,国内企业依赖进口,不仅成本高(进口靶材价格比国产高 20%-30%),还面临 “断供” 风险。

近年来,国内企业(如江丰电子、有研新材)通过技术突破,实现 5N 级铜靶、钽靶的规模化供应,部分产品进入中芯国际、长江存储等主流芯片厂供应链,国产化率从 2020 年的不足 10% 提升至 2024 年的 25% 以上。靶材国产化的突破,不仅降低了国内半导体企业的生产成本,更保障了供应链安全,为我国半导体行业从 “跟随” 向 “自主可控” 发展提供了关键支撑。

三、未来方向:溅射靶材向 “更高纯度、更优结构、更适配先进制程” 升级

随着半导体行业向 2nm 及以下制程、3D 集成、Chiplet(芯粒)等方向发展,溅射靶材也将迎来新的升级需求,主要聚焦三个方向:

1. 纯度再提升:向 7N 级迈进

2nm 及以下制程对杂质的容忍度更低(金属杂质需<0.1ppm),靶材纯度需从 6N 级向 7N 级突破,需通过 “电子束熔炼 + 区域熔炼 + 精密提纯” 组合工艺,进一步降低杂质含量,避免缺陷影响芯片性能;

2. 结构优化:适配 3D 集成与 Chiplet

3D 集成芯片需在垂直方向实现多层互连,对靶材的 “台阶覆盖率” 要求更高(需>90%),未来将开发 “梯度功能靶材”“纳米复合靶材”,通过调整靶材成分与微观结构,提升薄膜在复杂 3D 结构上的均匀性;

3. 成本控制:推动技术国产化与规模化

随着国内靶材企业产能扩张与技术成熟,将进一步降低高端靶材成本(预计 2025 年 6N 级铜靶国产化价格比进口低 30%),同时通过 “靶材回收再利用”(如从报废靶材中提取高纯度金属),提升资源利用率,降低半导体行业的整体材料成本。

结语

溅射靶材虽为半导体行业的 “微观材料”,却承载着芯片技术迭代的 “宏观使命”—— 它支撑着芯片从成熟制程向先进制程跨越,推动芯片性能不断突破、功耗持续降低,同时保障着行业供应链的安全稳定。随着半导体行业向更高精度、更复杂结构发展,溅射靶材的技术升级将持续成为行业进步的关键动力,而国产化靶材企业的崛起,也将为我国半导体产业的自主可控注入更强信心。

客服1

客服1