在半导体和微电子行业,器件微型化是核心趋势 —— 从微米级芯片到 7nm、3nm 制程,再到未来 1nm 技术,每次尺寸突破都离不开 “精准雕刻”。离子刻蚀机作为 “微观雕刻” 核心设备,以高能离子束精准移除材料,为微型电子器件生产奠定基础。本文解析其工作原理、核心应用及对未来制造的影响。

一、离子刻蚀机的工作原理:高能离子束的 “精准雕刻术”

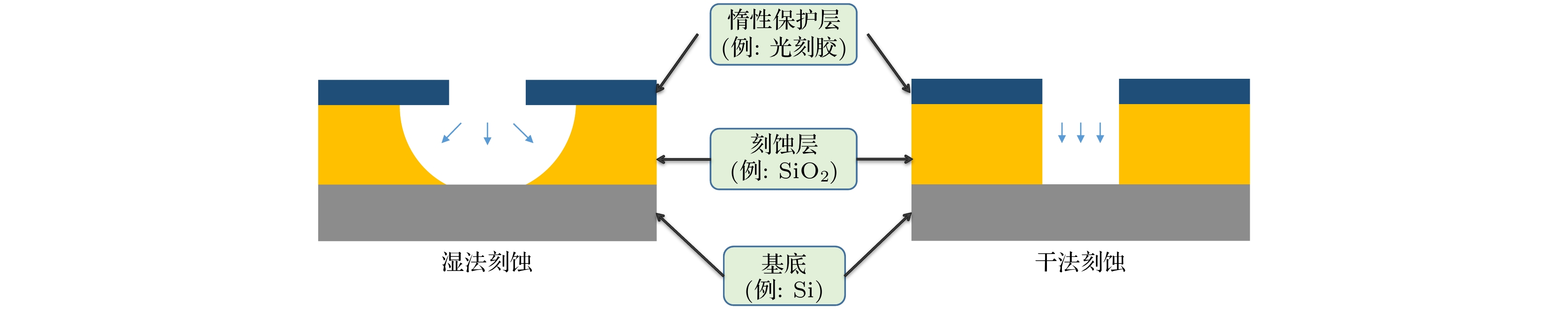

离子刻蚀机通过 “物理溅射” 与 “化学反应” 协同,在高真空环境中完成材料精准移除,分四步:

1. 离子源产离子:核心部件 “离子源” 电离氩气、氟气等产生等离子体,经电场加速、磁场约束,形成方向可控、能量稳定的高能离子束。

2. 光刻胶掩膜定位:晶圆表面覆盖 “光刻胶掩膜”,掩膜有与器件图案一致的镂空结构,保留区域被覆盖,待移除区域暴露,提供 “雕刻蓝图”。

3. 离子束轰击刻蚀:离子束轰击晶圆,暴露区域材料:物理刻蚀(如氩离子)靠动能使原子脱离;化学刻蚀(如氟离子)靠反应生成易挥发物,抽离后完成移除,两者结合兼顾速率与精度。

4. 控制刻蚀精度:实时监测离子束参数与时间,控刻蚀深度(纳米级精度,误差 < 1%);调整扫描路径保均匀性,避免器件失效。

简言之,离子刻蚀机以离子束为 “刻刀”、光刻胶为 “模板”,在晶圆上雕刻电子器件细微结构。

二、离子刻蚀机的核心应用领域

随着半导体器件缩小,离子刻蚀机成刚需设备,核心应用在三领域:

(一)集成电路(IC)制造:芯片微型化 “核心推手”

• 晶体管结构刻蚀:7nm 及以下制程中,FinFET、GAA 等极小结构,需多步精细刻蚀塑三维形态,保栅极与沟道精度,提升器件性能。

• 金属互联线刻蚀:在绝缘层刻十几纳米宽沟槽,填金属成导线,需侧壁垂直无毛刺,防短路或电阻过大。

先进制程芯片制造需多台离子刻蚀机协同,刻蚀步骤占总工艺 30% 以上,误差超 2nm 或致整批芯片报废。

(二)微机电系统(MEMS)制造:微型器件 “结构成型关键”

• 三维微结构刻蚀:用深反应离子刻蚀(DRIE),在硅晶圆刻深宽比 > 50:1 的沟槽(深几百微米、宽几微米),保侧壁垂直度与光滑度,制悬空梁、微腔体等。

• 异质材料刻蚀:调整离子参数,在硅基底刻金属时仅除金属、不损硅,保多材料结构匹配。

(三)光电子器件制造:高精度光学结构 “成型保障”

• 光栅结构刻蚀:在砷化镓等材料刻周期几百纳米的沟槽,保间距误差 < 5nm,确光栅分光效率与波长稳定。

• 光波导刻蚀:在绝缘材料刻 1-2 微米宽通道,控深度与侧壁光滑度,降光信号传输损耗(<0.1dB/cm)。

三、离子刻蚀机对未来制造技术的影响

半导体行业向 “更小、更高集成、更多功能” 发展,离子刻蚀机影响未来制造方向:

(一)推动芯片制程达 “原子级精度”

未来 1nm 及以下制程需原子级控制,离子刻蚀机可借 EUV 辅助刻蚀、实时原子层监测,实现纳米级以下控制,避原子级缺陷,为单原子晶体管奠基。

(二)赋能 “异质集成” 技术

未来异质集成(如逻辑与存储芯片集成)需离子刻蚀机兼容多材料刻蚀,同晶圆刻硅、碳化硅等,控刻蚀速率与选择比,破单一材料限制,提芯片功能密度。

(三)助力 “绿色低碳” 转型

优化离子源降能耗 20%-30%,开发无氟刻蚀工艺减有害气体,降废气处理成本与环境影响,契合行业 “碳中和”。

四、结语

离子刻蚀机是半导体微电子行业精细加工核心设备,技术水平定电子器件微型化与性能上限。从 IC 到 MEMS,从 7nm 到未来 1nm,它始终是技术突破关键。

微仪真空在离子刻蚀机真空系统设计、离子源适配有丰富经验,可提供一体化方案。未来,离子刻蚀机将向更高精度、兼容性、低碳方向发展,为电子制造注入动力。

客服1

客服1